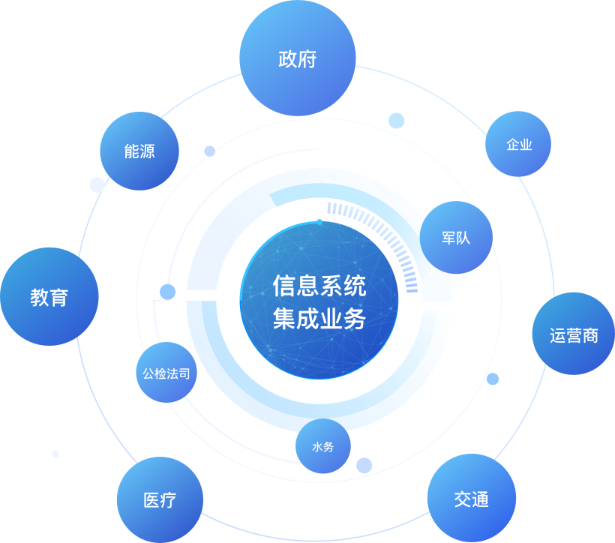

基于SoC與IP核復用技術實現綜合業務接入系統的集成電路設計

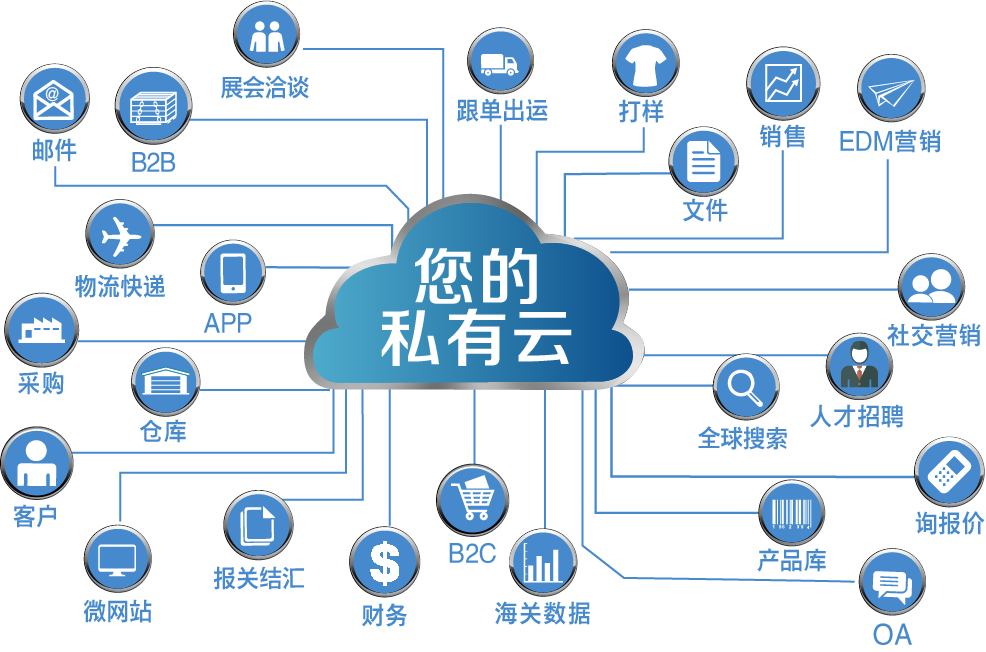

隨著通信技術的飛速發展,綜合業務接入系統作為連接用戶與核心網絡的關鍵樞紐,其性能、集成度與成本效益日益成為業界關注的焦點。傳統的多芯片分立解決方案已難以滿足高帶寬、多功能、低功耗及快速上市的需求。因此,采用片上系統(SoC)設計理念,結合成熟的IP核復用技術,成為實現下一代高性能、高集成度綜合業務接入系統芯片的關鍵路徑。

一、系統設計目標與架構規劃

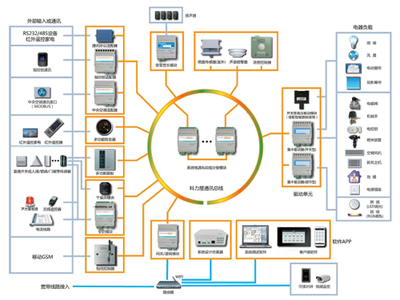

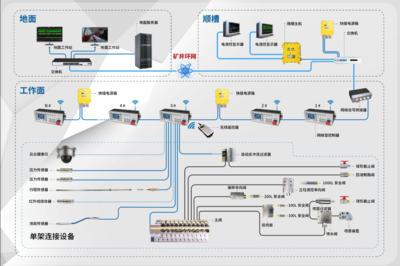

綜合業務接入系統需要同時處理多種業務流,如傳統的TDM語音、高速以太網數據、視頻以及新興的物聯網接入等。基于SoC的設計目標,是構建一個高度集成的單芯片解決方案。其核心架構通常包括:

- 中央處理單元:采用高性能、低功耗的處理器核(如ARM Cortex-A/M系列),負責系統控制、協議處理和業務調度。

- 通信接口子系統:集成多種物理層(PHY)接口IP,如xDSL、GPON/EPON、GE/10GE以太網、E1/T1等,以支持多樣化的接入媒介。

- 網絡處理與交換單元:包含數據包處理引擎、流量管理器和高速交換矩陣IP,實現業務流的分類、整形、轉發與匯聚。

- 存儲子系統:集成DDR控制器、SRAM、Flash控制器等IP,為系統運行和數據緩沖提供支持。

- 外圍與輔助單元:包括時鐘管理、電源管理、DMA控制器、通用IO等通用IP模塊。

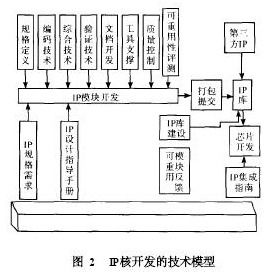

采用IP核復用技術,可以快速地從已驗證的IP庫中選取上述模塊,顯著縮短設計周期,降低開發風險和成本。

二、IP核的選擇、集成與驗證

IP核復用是SoC設計的基石。對于綜合業務接入系統,關鍵的IP核包括:

- 處理器IP:選擇經過市場廣泛驗證的處理器內核及配套的軟件開發工具鏈。

- 通信接口IP:選擇符合行業標準、性能達標的PHY和MAC層IP,確保與現有網絡的兼容性。

- 互連總線IP:采用高性能、可擴展的片上互連標準(如AMBA AXI),作為IP模塊間數據通信的“高速公路”。

集成過程并非簡單的堆砌。設計團隊需要:

- 進行精心的系統級建模與性能仿真,確保總線帶寬、內存訪問延遲等滿足嚴苛的業務需求。

- 解決各IP核之間的時鐘域、電壓域隔離與同步問題。

- 設計統一的系統控制與狀態寄存器映射,方便軟件驅動開發。

- 實施全面的硬件/軟件協同驗證,在流片前確保系統功能的正確性。

三、物理設計與系統集成考量

當所有數字邏輯設計完成后,將進入物理實現階段。此階段面臨的挑戰包括:

- 規模與復雜度:高度集成的SoC可能包含數千萬甚至上億門電路,對布局布線工具和設計方法學提出極高要求。

- 功耗與熱管理:集成眾多功能模塊,尤其是高速SerDes接口,功耗密度大。需要采用時鐘門控、電源門控、動態電壓頻率調節等技術進行精細化管理,并在封裝和散熱上做相應考慮。

- 信號完整性:高速信號在芯片內部及封裝內的傳輸需要嚴謹的仿真與設計,防止信號失真和串擾。

- 可測性設計:必須內置掃描鏈、內存BIST等DFT結構,以確保芯片制造后的高測試覆蓋率和良率。

成功的系統集成,意味著從架構規劃、IP集成、前端設計、后端物理實現到封裝測試的全流程無縫銜接,最終交付一顆功能完備、性能達標、可靠穩定的芯片。

四、優勢與展望

基于SoC和IP核復用技術設計綜合業務接入芯片,帶來了顯著優勢:

- 高集成度:將傳統板級的多芯片系統濃縮于單一硅片,大幅減小設備體積和功耗。

- 高性能:片內高速互連和硬件加速單元,遠超板級互連帶寬,提升了系統處理能力。

- 低成本:大規模集成降低了整體物料成本和PCB設計復雜度;IP復用節省了大量重復開發投入。

- 靈活性高:可通過軟件配置和可編程邏輯部分,適應不同應用場景和標準演進。

- 縮短上市時間:復用成熟可靠的IP核,使設計團隊能聚焦于系統創新與差異化開發,加速產品面市。

隨著5G固移融合、F5G全光接入及人工智能邊緣計算的發展,綜合業務接入系統芯片將朝著更高速率(如50G-PON、200G/400G以太網)、更高智能(內置AI處理單元)、更強安全(硬件級加密與信任根)的方向演進。SoC設計與IP復用技術,將繼續作為支撐這一演進的核心引擎,驅動接入網絡向更高效、更智能、更開放的方向持續發展。

如若轉載,請注明出處:http://www.uoschvv.cn/product/49.html

更新時間:2026-01-06 10:01:23